# **CMOS Compatible Thermal Management for Silicon Photonic Optical Phased Arrays**

<u>A. Krochin<sup>1,2</sup>; Dr. U. Scholz<sup>1</sup>; Prof. Dr. A. Zimemrmann<sup>2,3</sup></u> <sup>1</sup>Robert Bosch GmbH – Advanced Technologies and Micro Systems (CR/ATM) <sup>2</sup>Institute for Microintegration (IFM) - University of Stuttgart <sup>3</sup>Hahn-Schickard

## Motivation

Silicon photonic **optical phased arrays** (OPAs) are strongly **temperature dependent**:

> **Temperature** fluctuations, gradients and offsets **influence** functionality of **OPAs**<sup>1</sup>.

#### Results

> **Confirmed** concept **feasibility** by fabrication and characterization of thermal demonstrators.

> Novel **thermal management** solutions are **required** to guarantee proper functionality of silicon OPAs <sup>2,3</sup>.

### Background

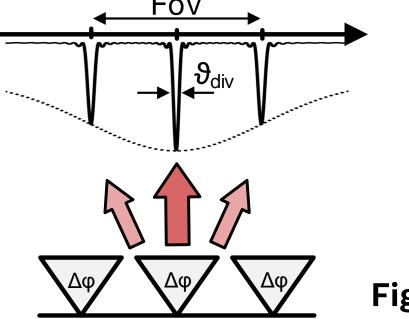

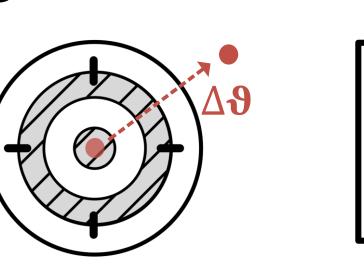

> Optical phased arrays are phase sensitive, solidstate **beam steering devices**

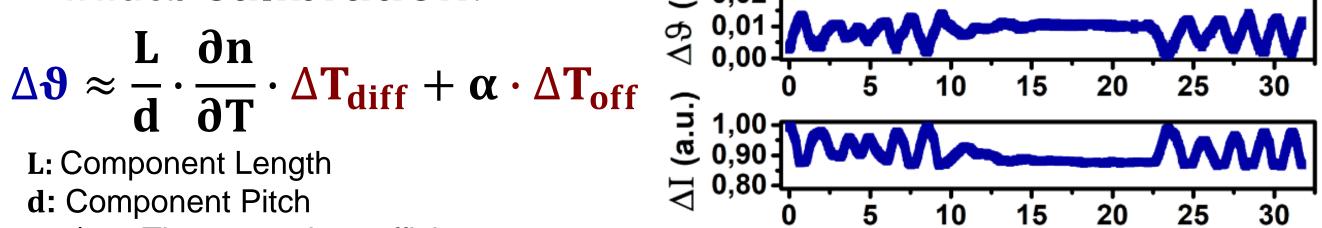

Figure: Left) OPA Radiation Pattern Top) OPA Angular Error

> Strength of the temperature influence depends on OPA **implementation**<sup>1</sup> and  $\alpha$  **depends** on OPA initial calibration.

ပ္လွ် 22,8 ၃ 22,4

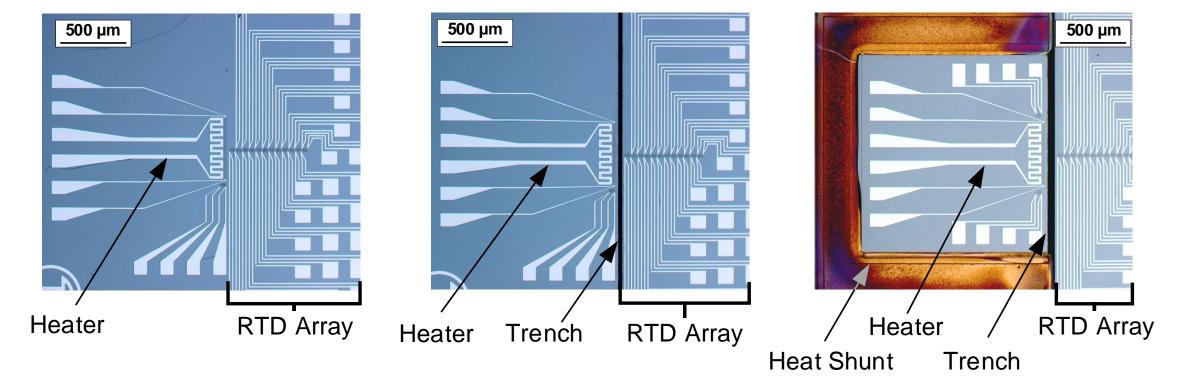

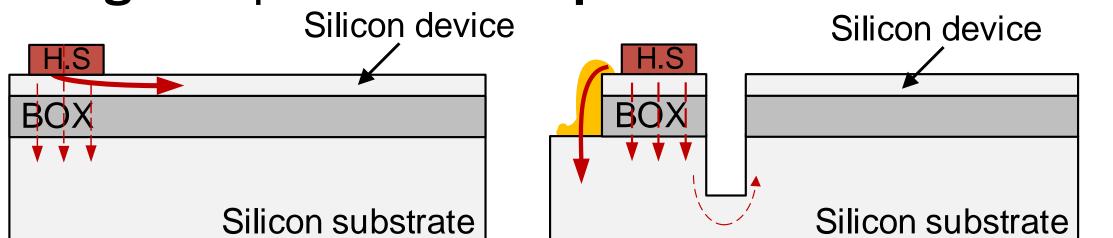

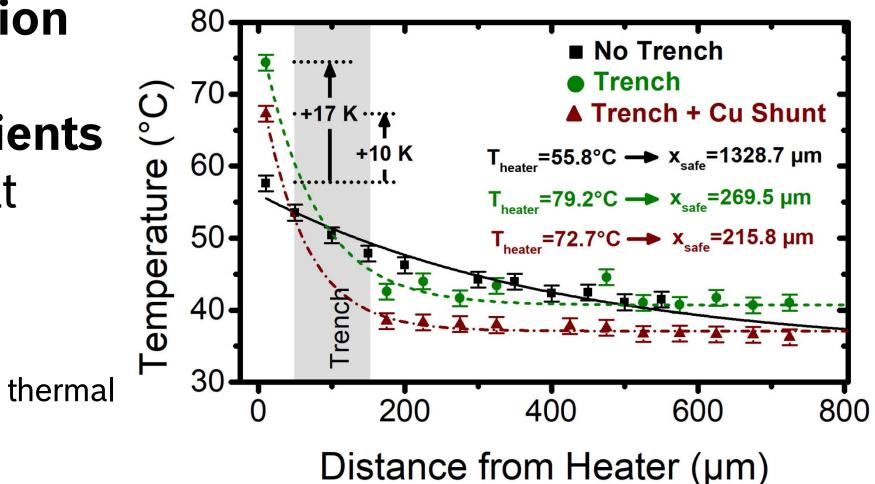

**Figure:** Left) Reference thermal demonstrator. Center) Thermal demonstrator with trench. Right) Thermal demonstrator with trench and heat shunts. Figure adapted from <sup>2</sup>

> Trenches reduce safe distances  $(x_{safe})$  at the cost of an increased heat source temperature.

| width →               | <u>Safe distance</u> x <sub>safe</sub> |                      |                       |   | <u>Heat source temperature</u> |                      |                       |

|-----------------------|----------------------------------------|----------------------|-----------------------|---|--------------------------------|----------------------|-----------------------|

| ↓ depth               | <b>25</b> μ <b>m</b>                   | <b>50</b> μ <b>m</b> | <b>100</b> μ <b>m</b> |   | <b>25</b> μ <b>m</b>           | <b>50</b> μ <b>m</b> | <b>100</b> μ <b>m</b> |

| <b>0</b> μ <b>m</b>   | <b>1393</b> μ <b>m</b>                 |                      |                       | - | <b>74.7</b> °C                 |                      |                       |

| <b>119</b> μ <b>m</b> | 913 µm                                 | 777 µm               | 768 µm                |   | 81.0 °C <                      | 88.1 °C              | 92.7 °C               |

| <b>254</b> μ <b>m</b> | 259 µm                                 | 273 µm               | 473 μm                |   | 95.3 °C                        | 92.0 °C              | 96.1 °C               |

| <b>330</b> μ <b>m</b> | <b>217</b> μ <b>m</b>                  | 234 µm               | 279 µm                | _ | 103.1 °C                       | 105.0 °C             | <b>111.2</b> °C       |

**Table:** Comparison of the calculated safe distance x<sub>safe</sub> and the heat source temperature for different trench widths and trench depths.

> Heat shunts provide a high thermal conductivity

**connection** between heat source region and silicon substrate → preferred path for

$\partial n/\partial T$ : Thermo-optic coefficient  $\alpha$ : Offset / Calibration factor

**Figure:** Response of a prototype OPA towards room temperature fluctuations.

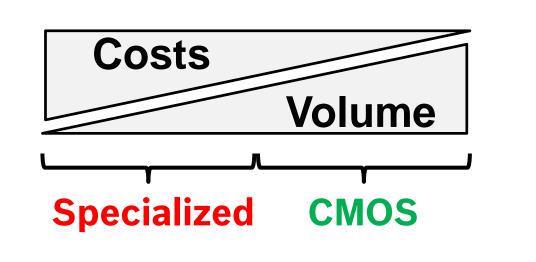

> CMOS compatible thermal management solutions are **required**.

Time (h)

**Δθ** depends on  $\Delta \phi$

$\Delta \phi$  depends on  $\Delta n$

$\Delta n$  depends on  $\Delta T$

25

20

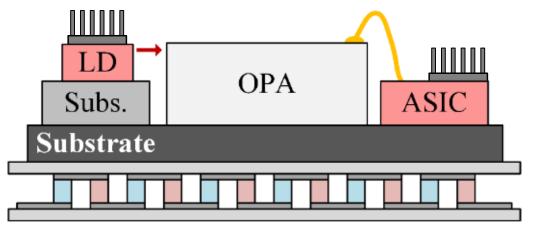

**Figure:** OPA system with specialized thermal management solutions

## Approach

> Perform **structural modifications** within the photonic IC to change the preferred heat paths.

emperatur heat dissipation  $\rightarrow$  reduction of thermal resistance

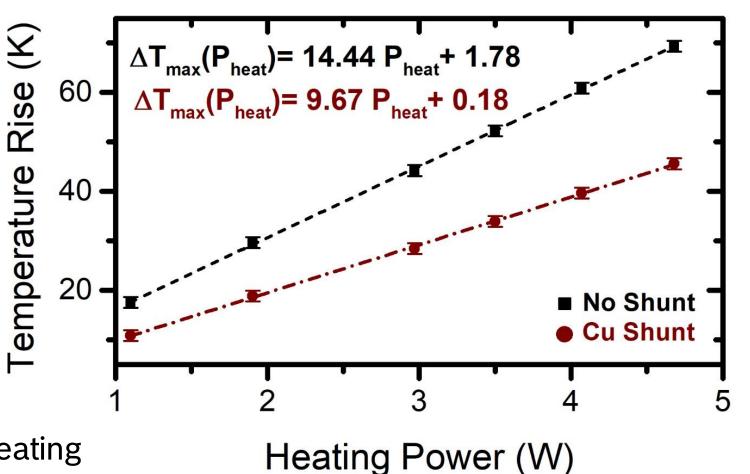

**Figure:** Temperature rise for different heating powers with and without heat shunts.

**Combination** of trenches and heat shunts provide a

convenient solution to **reduce** on-chip temperature gradients and **improve** heat dissipation

Figure: Temperature profile on thermal demonstrator.

Conclusions

Figure: Left) Conventional Photonic IC. Right) Photonic IC with Heat Shunts and Trenches.

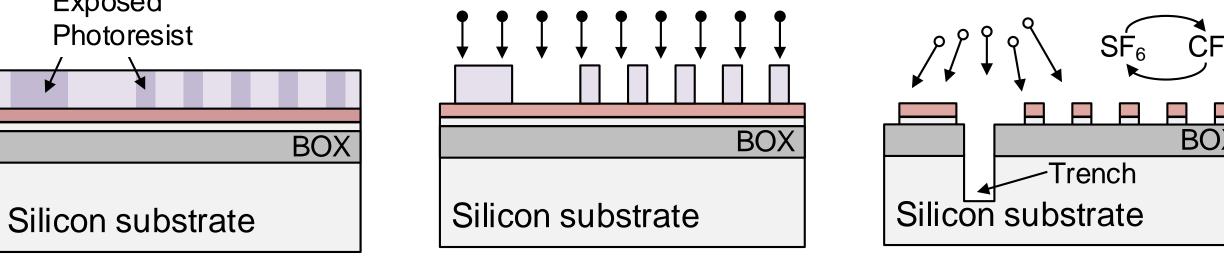

> Alternate **CMOS processes** (e.g. PVD, CVD, IBE, DRIE, Lithography) for **fabrication** of thermal **demonstrators**.

Exposed **Photoresist**

Figure: Left) Lithography Step. Center) IBE Step. Right) DRIE Step.

1: Krochin et al., IEEE Photonics Journal, Vol. 12 No. 2 (2020) 2: Krochin et al., MDPI Photonics, Vol. 7 No. 1 (2020) 3: Krochin et al., IEEE Photonics Journal, Vol. 11 No. 4 (2019)

**Contact: Andrei Krochin, Robert Bosch GmbH** PedroAndrei.KrochinYepez@de.bosch.com

- > CMOS compatible solutions for thermal management of silicon photonic OPAs were **successfully demonstrated**.

- > Trenches reduce  $x_{safe}$  by over 80 %

- $\rightarrow$  **Trade-offs** between trench width, depth and reduction of temperature gradients were **identified**.

- > Heat Shunts reduce thermal resistance by over 30 %.

- > Modular solutions for thermal management can be applied beyond OPAs for any temperature sensitive photonic IC.