## Photonic Integrated Circuit Platform using III-V on SiC Wafer

## Mitsuru TAKENAKA\*, Shinichi TAKAGI

Department of Electrical Engineering and Information Systems, The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo, 113-8656, Japan \* takenaka@mosfet.t.u-tokyo.ac.jp

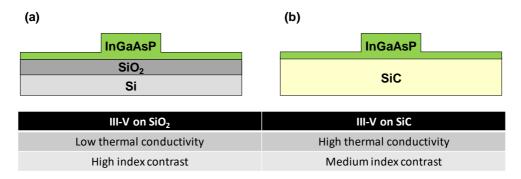

Photonic integrated circuits (PICs) based on a high-index-contrast waveguide have paved a pathway to large-scale integration for photonics in the past ten years. Similar to Si photonics, we have investigated III-V CMOS photonics platform based on III-V on insulator (III-V-OI) wafer as shown in Fig. 1(a) [1]. We are able to fabricate ultrasmall InP PICs owing to the high-index contrast between III-V layers and SiO<sub>2</sub> buried oxide (BOX). Like Si-on-insulator (SOI) wafers, III-V-OI wafers can be fabricated by using direct wafer bonding [2]. Thus, we have demonstrated various passive components based on InGaAsP strip/rib waveguides including micro bends [2], arrayed waveguide gratings [2], and grating couplers [3]. Active components including modulators/switches [4], laser didoes (LDs) [4, 5], photodetectors [6, 7], and variable optical attenuators [8] have also been reported so far.

While the III-V-OI structure provides significant impact on device miniaturization for InP photonics, its low thermal conductivity is one of the drawbacks particularly for LDs. When free carriers are injected into an InP-based waveguide on the III-V-OI wafer, heat generated by current injection hardly dissipates through the thick  $SiO_2$  where the thermal conductivity is quite low. Thus, the maximum power emitted from a single LD is limited to a few mW when its cavity length is approximately  $100~\mu m$  [4]. Moreover, the poor thermal dissipation restricts the density of active devices on a single chip.

In this paper, we propose to use a SiC BOX instead of  $SiO_2$  as shown in Fig. 1(b). Since the thermal conductivity of SiC is more than 100 times greater than that of  $SiO_2$ , we expect that the heat dissipation can be improved drastically by introducing a III-V on SiC wafer. On the other hand, the medium refractive index contrast between III-Vs and SiC arises concern about device miniaturization. Here we numerically analyze an InGaAsP waveguide on SiC in terms of bend loss and heat dissipation for feasibility study.

Fig. 1. Schematic of InGaAsP rib waveguide on (a) conventional III-V on insulator wafer and (b) III-V on SiC wafer proposed in this paper.

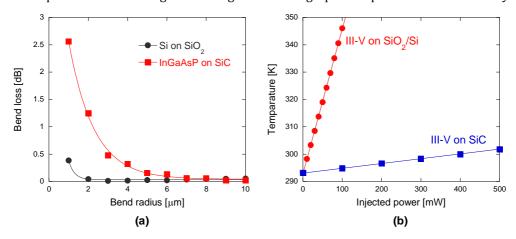

First, we evaluated the propagation loss of a  $90^{\circ}$  bend using 3D FD-TD simulation. Figure 2(a) is a comparison of bend loss of a Si strip waveguide on  $SiO_2$  and InGaAsP strip waveguide on SiC as a function of the bend radius. While the medium index contrast of the InGaAsP on SiC waveguide resulted in the larger bend loss than that of the Si waveguide with the small bend radius, the difference in bend loss was negligible when the bend radius was greater than 7  $\mu$ m, which is sufficient for large scale integration in most of PICs. Then, we analyzed the heat dissipation in the III-V on  $SiO_2/Si$  and III-V on SiC wafers as shown in Fig. 2(b). It was found that the increase in the device temperature of the III-V on SiC was 30 times smaller than that of the III-V on  $SiO_2/Si$ . Thus, the III-V on SiC platform enables large scale integration and high-power operation simultaneously.

Fig. 2. (a) Bend loss of InGaAsP strip waveguide on SiC and Si strip waveguide on SiO<sub>2</sub> and (b) device temperature with injected power into III-V rib waveguide on SiO<sub>2</sub> and SiC.

Acknowledgement: This work was supported in part by a Grant-in-Aid for Young Scientists (A) from MEXT.

## References

- [1] M. Takenaka and Y. Nakano, "InP photonic wire waveguide using InAlAs oxide cladding layer.," *Opt. Express*, vol. 15, no. 13, pp. 8422–7, 2007.

- [2] M. Takenaka, M. Yokoyama, M. Sugiyama, Y. Nakano, and S. Takagi, "InGaAsP Photonic Wire Based Ultrasmall Arrayed Waveguide Grating Multiplexer on Si Wafer," *Appl. Phys. Express*, vol. 2, no. 12, p. 122201, Nov. 2009.

- [3] M. Takenaka, M. Yokoyama, M. Sugiyama, Y. Nakano, and S. Takagi, "InGaAsP Grating Couplers Fabricated Using Complementary-Metal-Oxide-Semiconductor-Compatible III-V-on-Insulator on Si," *Appl. Phys. Express*, vol. 6, no. 4, p. 42501, Apr. 2013.

- [4] S. Matsuo, T. Fujii, K. Hasebe, K. Takeda, T. Sato, and T. Kakitsuka, "Directly modulated buried heterostructure DFB laser on SiO<sub>2</sub>/Si substrate fabricated by regrowth of InP using bonded active layer," *Opt. Express*, vol. 22, no. 10, pp. 12139–12147, May 2014.

- [5] D. Inoue, J. Lee, K. Doi, T. Hiratani, Y. Atsuji, T. Amemiya, N. Nishiyama, and S. Arai, *Appl. Phys. Express*, vol. 7, no. 7, p. 72701, Jul. 2014.

- [6] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, IEICE Electron. Express, vol. 11, no. 16, pp. 20140609–20140609, 2014.

- [7] L. Shen, Y. Jiao, W. Yao, Z. Cao, J. P. van Engelen, G. Roelkens, M. K. Smit, and J. J. G. M. van der Tol, "High-bandwidth uni-traveling carrier waveguide photodetector on an InP-membrane-on-silicon platform," *Opt. Express*, vol. 24, no. 8, p. 8290, 2016.

- [8] J.-K. Park, J.-H. Han, M. Takenaka, and S. Takagi, MRS Adv., vol. 1, no. 48, pp. 3295–3300, May 2016.