## Design and Optimization of a High Speed Slow-Light Silicon Modulator in the O-Band

## Andrea ZANZI1\*, Pablo SANCHIS1, Javier MARTI1, Antoine BRIMONT1

<sup>1</sup>Valencia Nanophotonics Technology Center, Universitat Politècnica de València Building 8F | 1st Floor, Camino de Vera, s/n, 46022 Valencia, Spain \* anzan@ntc.upv.es

The ever-growing increase in global internet traffic imposes significant challenges in data centre (DC) operators equipment manufacturers. These modern DCs utilized hundreds of thousands of servers in several hierarchy layers, which require an efficient interconnection network that have to be both low-cost and energy-efficient. This is precisely where silicon photonics can play a key role. Indeed, Silicon-on insulator (SOI) technologies is currently considered as one of the most promising platforms to achieve high density levels of integration of photonic devices at low cost, owing to its high-index contrast and compatibility with mature complementary metal-oxide semi-conductor (CMOS) fabrication process.

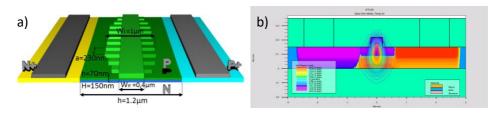

In this paper, we present the design of a compact slow-light modulator in a Mach-Zehnder configuration. The proposed slow light modulator device exploits the silicon free-carriers plasma dispersion effects produced by a reverse-biased vertical PN junction in a shallow etched configuration (Fig. 1(a)) [1]. In this configuration, the optical mode overlaps the carrier depletion region in an optimized fashion (Fig 1(b)). Additionally, the vertical pn junction is defined by the implantation energy with one single lithography step rather than using two masks that must be accurately positioned in the middle of the waveguide [2] as in laterally/horizontally formed pn junction. This makes our optical device cost-effective and more tolerant to potential fabrication variations, with a better yield across the processed wafer. The combination a highly efficient pn with the use of properly apodized slow-light waveguides will dramatically improve the performance of the modulator in terms of footprint and power consumption, making it compatible with advanced low power CMOS electronics

Fig. 1 – Fundamental schematics of the slow-light modulator and 2D-cut of the PN junction

The design of the proposed device consists of several steps. First, we model the phase shifter, using ATHENA and ATLAS, respectively process and device simulators by

SILVACO. For a complete design and analysis of the structures, finely meshed 3D FDTD and plane wave expansion (PWE) simulations have been performed. The PWE simulations allow studying the dispersion relation of the periodic structure followed by 3D FDTD in order to obtain the transmission spectra. The studied structure feature the following parameters: period (a=230 nm), w<sub>e</sub>=400nm, w<sub>i</sub>=1000nm, h=70nm and H=150nm (Fig.1(a)). The use of slow light will increase the efficiency [5] proportionally to the slow down factor which is given by the ratio between the group index of the optical mode in the normal "fast-light" regime (n<sub>g</sub> ~3.64) and the slow-light "Bloch-mode" propagating with a moderately high group index (n<sub>g</sub>~10-20). As a result, we obtain an enhancement factor ranging from 2.75 to 5.5. When translated in terms of efficiency, the figure of merit drops by the same factor, reaching record values below 0.1V\*cm.

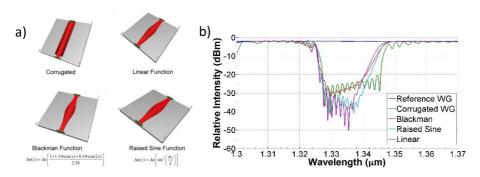

Fig. 2 – (a) Pictures of the tapered fast-to-slow-light transitions. (b) Spectral outputs of the three different tapers with apodization functions and corrugated waveguide (as reference).

The main issue linked with slow-light propagation is the coupling between light travelling in a standard single mode silicon waveguide and the periodic one. A major issue when dealing with slow light propagation is finding a way to achieve a gradual transition from the fundamental waveguide mode to the slow light mode of the periodic waveguide. To overcome this issue, the use of tapers and/or apodization technique is mandatory. Here, we designed and simulated three preliminary different apodization schemes to ensure smooth fast-to-slow light transitions (Fig. 2(a)). The resulting spectra are shown in Fig. 2(b). We can observe a clear improvement can be seen on the fast-to-slow transitions for the three apodization schemes when compared with the untapered corrugated waveguide. Further designs are under development implementing algorithms such as "Particle Swarm Optimization" and "Convex Optimization".

In conclusion, we have shown the promising use of slow light a means to enhance dramatically the efficiency of carrier depletion modulator with optimized apodization schemes to minimize the loss penalty produced by the fast-to-slow light transitions making slow light modulators readily compatible with advanced low power CMOS electronics.

**Funding:** H2020-ICT-2015, n° 688544, "L3MATRIX". Spanish Funding from "Comunitat Valenciana" under Grisolia Program.

## References

- [1] A. Brimont, et al, "High speed silicon electro-optical modulators enhanced via slow light propagation," *Opt. Express* 19, 20876-20885 (2011).

- [2] Brimont, A., et al. "Compact and efficient silicon 2×2 switches based on a reverse biased vertical pn junction." *Group IV Photonics (GFP), 2014 IEEE*, vol., no., pp.159-160, 27-29 Aug.